Please select your location and preferred language where available.

以创新的2mm闪存封装技术引领AI革命

将32个闪存芯片集成于单个封装之中

翻译源: EE Times Japan

翻译自 EE Times Japan 2025年8月20日发布文章

本文经过EE Times Japan同意后转载

部门名称、头衔为采访当时的内容。

AI的飞速发展加速了对闪存容量的需求。铠侠将32个2Tb的闪存芯片集成于高度小于2mm的封装中,成功研发出容量高达8TB的闪存。我们采用晶圆减薄等先进的后端工艺,成功实现了这一存储器解决方案。

随着AI的扩展,数据存储比以往任何时候都更加重要

由于AI服务的高速发展,数据中心的存储和处理需求呈指数级增长趋势。近年来,除了生成式AI的爆炸性增长之外,应对AI幻觉问题的RAG(检索增强生成)技术的应用也日益增多,进一步加速了数据的增长。因此,用于数据中心的SSD以及构成SSD的闪存变得不可或缺。

铠侠株式会社封装与测试技术执行官田窪知章说道:“随着数据量的指数级增长,对更高性能、更大容量SSD的需求也在加速。”此外,对降低功耗和成本的需求也日益增加。铠侠已预见到这些趋势,并进行了SSD及其闪存性能和容量改进的规划。

为了提升性能和容量,铠侠于2024年研发了采用第八代 BiCS FLASH™(注1)3D 闪存技术的 2Tb QLC(四级单元)存储器,将3D闪存技术推向了新的高度。这款存储器采用COMS直接键合到存储阵列(CBA)架构。该项技术使用不同的晶圆来制作负责存储单元控制的CMOS电路与存储单元阵列,再将两枚晶圆粘贴在一起。现在,通过将16个第八代 BiCS FLASH™ 芯片堆叠在单个存储器封装之中,可以实现32Tb或4TB(注2)容量。

通过先进的存储器封装工艺实现8TB容量

虽然CBA技术是提升闪存性能的关键,但半导体晶圆制造工艺的进步必须与后端封装工艺的发展保持同步。后端工艺包括堆叠闪存芯片并将其集成于封装之中。

闪存容量的增加由两个因素驱动:一是通过改进晶圆制造工艺来提高单个芯片的容量,二是通过改进后端工艺来提高每个封装的容量。为了满足对更大容量闪存的需求,必须在晶圆制造和后端工艺两方面都进行改进。此外,由于近年来晶圆制造工艺变得越来越复杂,后端工艺的改进也迫在眉睫。

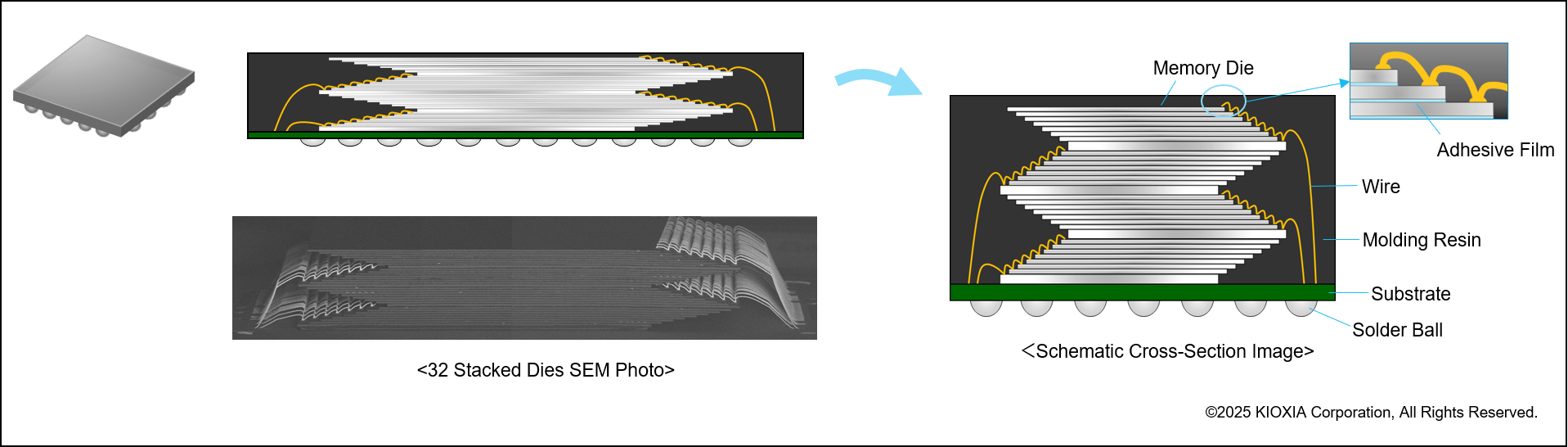

通过研发先进的后端工艺,铠侠成功将32个2Tb容量的闪存芯片堆叠到高度小于2mm的单个封装之中(JEDEC标准尺寸:11.5 x 13.5 mm)。实现在单个闪存单元上提供8TB容量这一里程碑之后,铠侠在SSD扩容方面又迈出了重要得一步。“我们将铠侠所有的后端工艺和专业知识都融入到了这款产品之中,”田窪知章先生说道,“更具体地说,我们采用三种不同的技术实现如此高的容量:高精度晶圆加工、材料设计和引线键合。”

以创新的封装技术将32个芯片堆叠在仅2mm高的封装之中

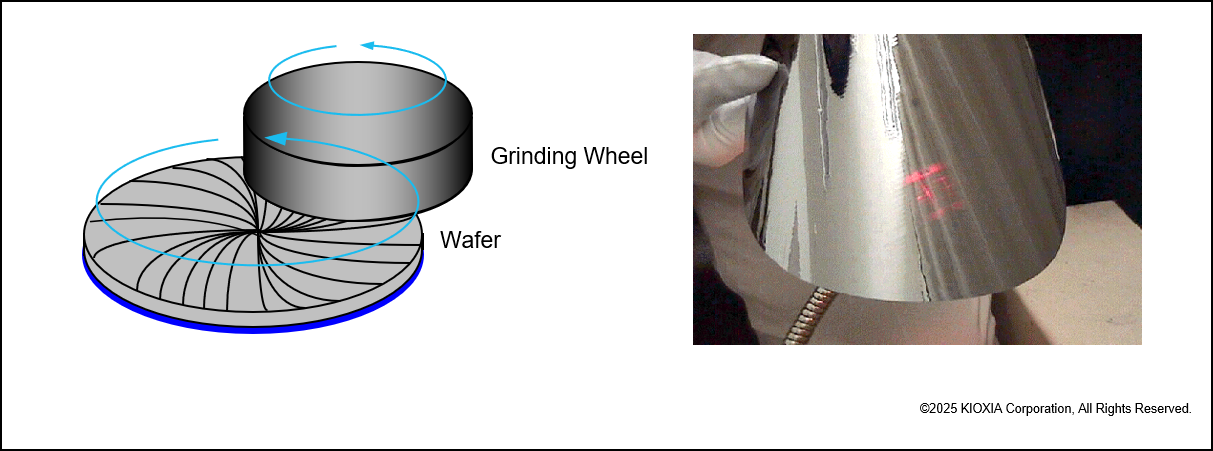

第一项技术是高精度晶圆加工。该技术是晶圆减薄的关键,以便增加封装中可堆叠的芯片数量,从而增加每个封装的存储容量。

铠侠将300mm晶圆的厚度从0.8mm研磨至30-40μm,使晶圆厚度精度控制在0.1μm。要理解该工艺的精细程度,不妨想象一下,将一个滑冰场(60 x 30m)大小的巨大冰块均匀研磨至仅5mm的厚度,且厚度公差不超过0.5mm。

如果单个芯片的厚度增加2μm,堆叠32层将导致总厚度增加64μm,从而使芯片和引线键合线暴露在封装之外,无法保证产品质量。将晶圆尽可能减薄,可增加芯片堆叠的层数,同时确保质量。

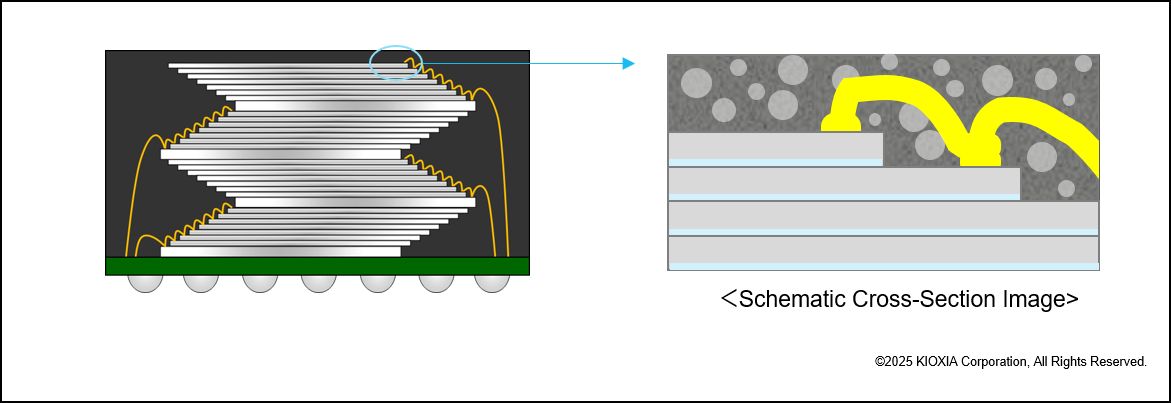

第二项技术与材料设计相关,即制造用于封装的模塑树脂。在封装过程中,堆叠的芯片通过引线键合技术与基板相连,从而实现电气互连。然后,将模塑树脂倒入模具中密封并完成封装。其中,最顶层的堆叠芯片和引线与封装顶部之间的厚度(即芯片上方的树脂厚度)非常关键。如果厚度不足,芯片和引线就会暴露在外,影响产品的质量和可靠性。因此,芯片上方模塑树脂的厚度必须精确控制在100μm。这项工艺对模塑树脂的物理特性提出了严苛的要求,即必须在流动性与填充性之间达到最佳平衡。由于这种模塑树脂的研发并非易事,因此铠侠与材料制造商密切合作,设计出精确的材料。

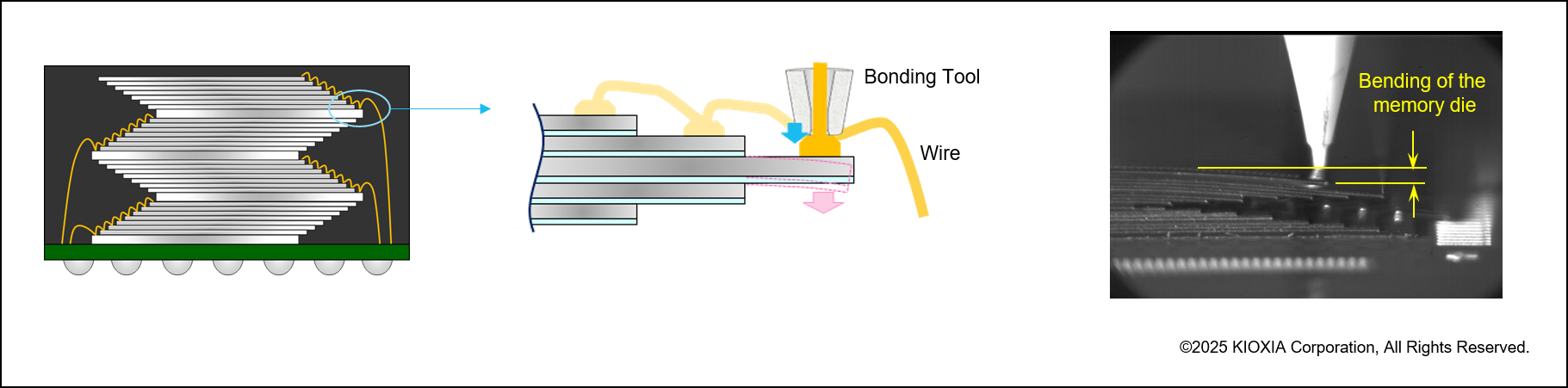

第三项关键技术是引线键合。芯片以阶梯式偏移层层堆叠,为引线键合留出空间。部分芯片形成了屋檐状的悬伸结构,在引线键合的压力下极易弯曲。因此,引线键合工艺必须进行极为精准的应力控制,以防止芯片因受力过大而破裂。铠侠不断研发满足这些要求的规范,并将其融入制造工艺之中。“引线键合的关键在于,我们必须逐步控制应力以防止裂纹的产生,必须在极短的键合时间内完成极其精密的调整。而实现这种精密控制的技术,正是铠侠的优势之一,也是我们先进封装技术的基础,”田窪知章先生强调。

旨在优化和集成所有材料与工具的封装工艺

仅凭上述三项技术,铠侠封装工艺的精密与复杂性已可见一斑。然而,这远非全部,其背后是许多其他技术元素的持续优化,从用于芯片堆叠的粘合膜,到旨在确保信号完整性、电源完整性和可靠性的封装基板设计。此外,随着堆叠层数的增加,新的挑战也接踵而至,例如芯片翘曲,以及因顶层与底层芯片间的巨大高度差而造成的引线键合机对焦困难等问题。为了解决这些问题,我们对所有材料和工具都进行了优化。铠侠高密度闪存的成功,正是建立在对无数工艺细节日复一日的优化与集成之上。

为满足市场对更大容量的渴求,铠侠正致力于下一代封装技术的研发。“铠侠的优势在于,我们对材料和设备有着深入的了解,从晶圆制造、闪存和SSD研发到封装工艺等所有部门之间进行积极、开放的讨论。例如,我们正在合作研发堆叠结构,以增加单个封装中堆叠芯片的数量,比如双子塔式的结构,”田窪知章先生指出。

通过先进的后端工艺推动AI进步

田窪知章先生说:“以人体来举例,半导体(例如CPU)相当于大脑、心脏和内脏等重要器官。而连接这些半导体和电子元件的封装技术(即后端工艺)则相当于血管和肌肉。有了血管和肌肉,所有器官才能有机地运作,整个身体的各项功能才能得到优化和最大化——这就是封装技术的精髓。我认为我们目前所面临的挑战是,如果不改进后端工艺就难以提升性能。”

仅在短短一年之内,铠侠闪存封装中的堆叠芯片数量就从16个增加一倍,达到了32个。“早在八年前,我们就曾考虑过 32 Die 堆叠技术,但由于当时市场需求不足,所以没有商业化,”田窪知章先生说。如今的情形已大不相同。随着AI大趋势的持续,市场对更大容量闪存的需求将强势爆发。“铠侠的责任是快速为客户提供集大容量、高速度、小尺寸与低能耗于一体的闪存和SSD产品,”田窪知章先生强调。AI时代的变更正在加速,铠侠将持续创新,通过先进的闪存晶圆制造和封装工艺满足新时代的需求。

Notes

- 本文所述信息在采访时是准确的。

注1:“BiCS FLASH”为铠侠株式会社的商标。

注2:通常,存储芯片的容量单位为比特(bit),而存储产品的容量单位为字节(byte)(8比特 =1字节)。

另请查阅

高精度的双晶圆键合为高密度化存储器带来新价值的3D闪存

近年来,各家闪存厂商尤为着力的,就是对通过存储单元“高层数”方式以提高存储密度的技术的开发。每当有新一代闪存产品发布,层数就会有所增加,有些产品甚至已经超过了200层。但是,铠侠存储器事业部部长井上敦史则表示:“存储单元的‘高层数’只不过是大容量化和存储密度升级的方法之一,我们并不拘泥于积层数的增加。”