Please select your location and preferred language where available.

铠侠研发核心技术,为高密度、低功耗 3D DRAM 的实用化铺平道路

展示高度可堆叠性氧化物半导体晶体管技术

- 2025 年 12 月 10 日

- 铠侠株式会社

全球存储解决方案领导者铠侠今日宣布,已成功开发出高度可堆叠的氧化物半导体沟道晶体管,为实现高密度、低功耗的3D DRAM实用化铺平了道路。该成果已于 12 月 10 日在美国旧金山举办的 IEEE 国际电子元件会议(IEDM)上发布,有望降低各种应用的功耗,例如 AI 服务器和物联网产品。

在 AI 时代,海量数据处理需求激增,市场对大容量、低功耗 DRAM 的需求日益增长。传统的DRAM技术正在达到内存单元大小缩放的物理限制,促使研究内存单元的3D堆叠以提供额外的容量。传统 DRAM 技术正逼近存储单元尺寸微缩的物理极限,促使业界将目光投向通过存储单元 3D 堆叠来提升容量的研究。但在堆叠存储单元中,若继续沿用传统 DRAM 的单晶硅作为晶体管沟道材料,不仅会推高制造成本,还会导致刷新存储单元所需的功耗随容量增加而成比例上升。

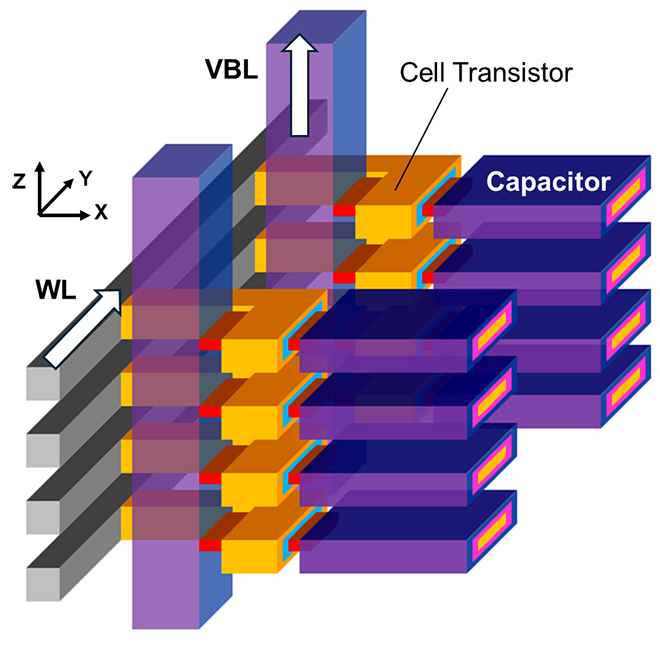

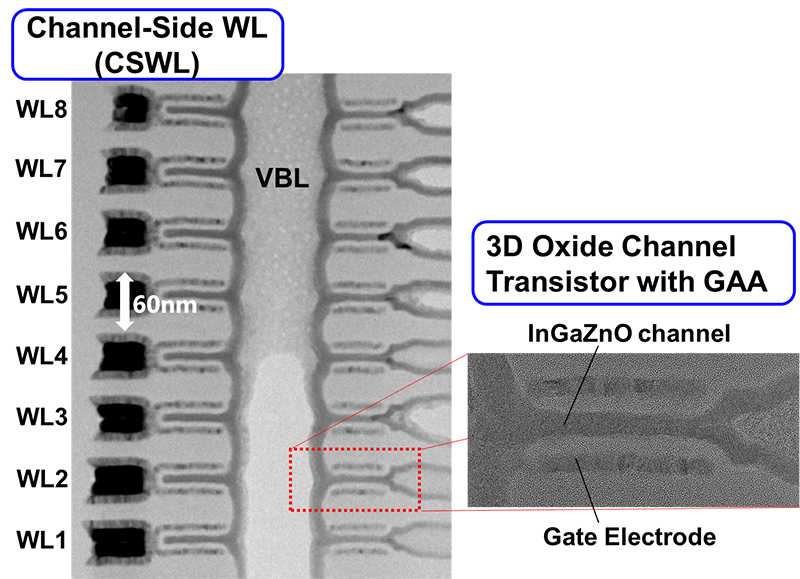

在去年的 IEDM 上,我们发布了 OCTRAM(氧化物半导体晶体管 DRAM)技术,该技术主要采用由氧化物半导体组成的垂直晶体管。今年,我们则展示了高度可堆叠性氧化物半导体晶体管技术,该技术使 OCTRAM 的 3D 堆叠成为可能。我们已成功验证 8 层堆叠晶体管能够正常运行。

新技术采用成熟的氧化硅和氮化硅薄膜交替堆叠工艺,将氮化硅区域置换为氧化物半导体(InGaZnO),从而同时形成垂直层水平堆叠的晶体管。此外,我们还引入一种创新的 3D 存储单元结构,能够有效缩小垂直节距。凭借这些创新的制造工艺和结构设计,业界有望克服实现存储单元 3D 堆叠所面临的成本难题。

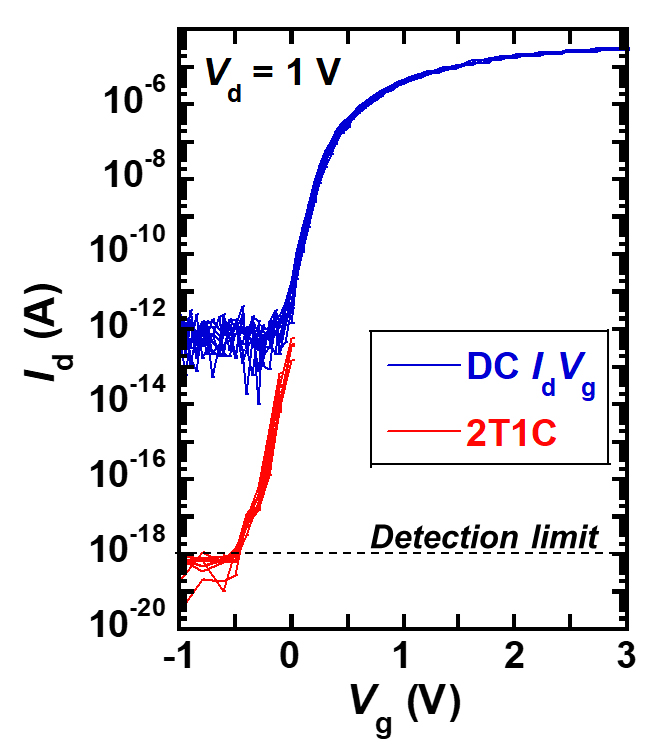

此外,得益于氧化物半导体极低的关断电流特性,DRAM 的刷新功耗将显著降低。实验数据显示,我们已经展示了通过替代工艺(OCTRAM)形成的水平晶体管,兼具高导通电流(> 30μA)和超低关断电流(< 1aA,10^-18A)的优异性能。在此基础上,我们成功研制出 8 层堆叠的水平晶体管,并验证该结构内部晶体管均能正常运行。

铠侠将继续该技术的研发,力争早日实现 3D DRAM 在现实场景中的应用部署。

- This announcement has been prepared to provide information on our business and does not constitute or form part of an offer or invitation to sell or a solicitation of an offer to buy or subscribe for or otherwise acquire any securities in any jurisdiction or an inducement to engage in investment activity nor shall it form the basis of or be relied on in connection with any contract thereof.

- Information in this document, including product prices and specifications, content of services and contact information, is correct on the date of the announcement but is subject to change without prior notice.